综合类型的PCB阻抗设计

**

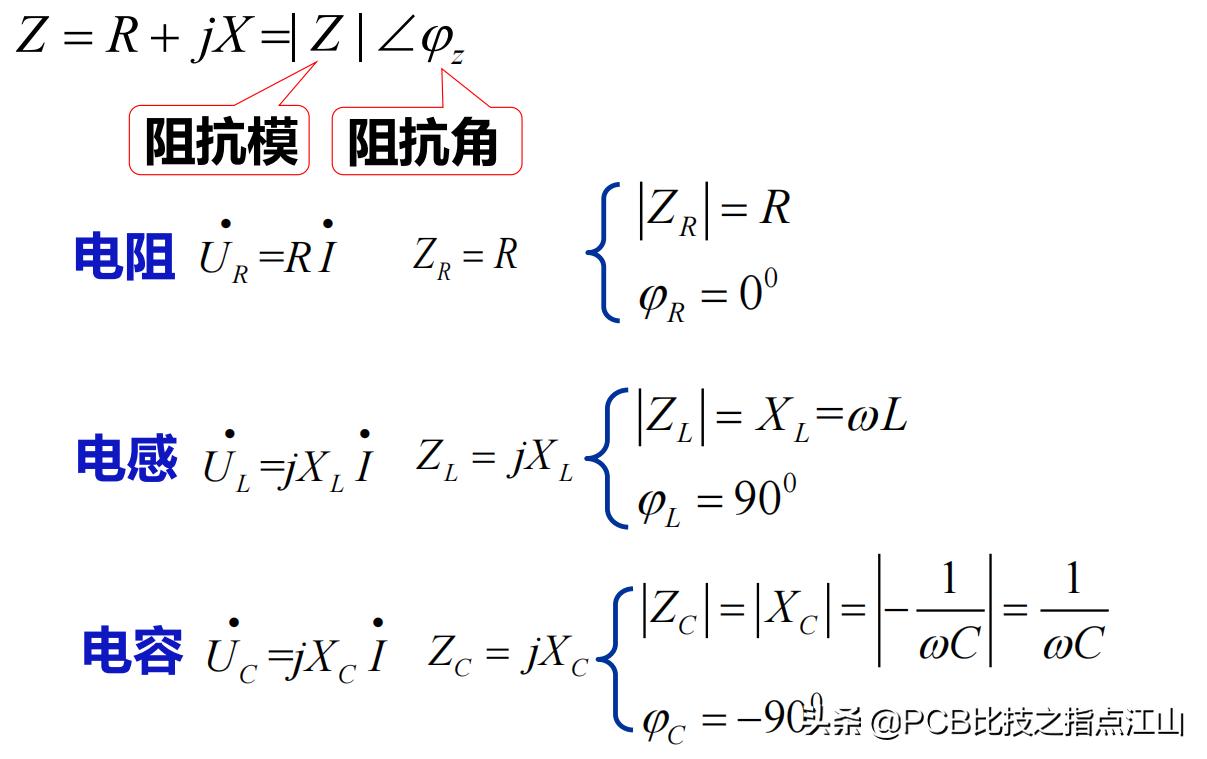

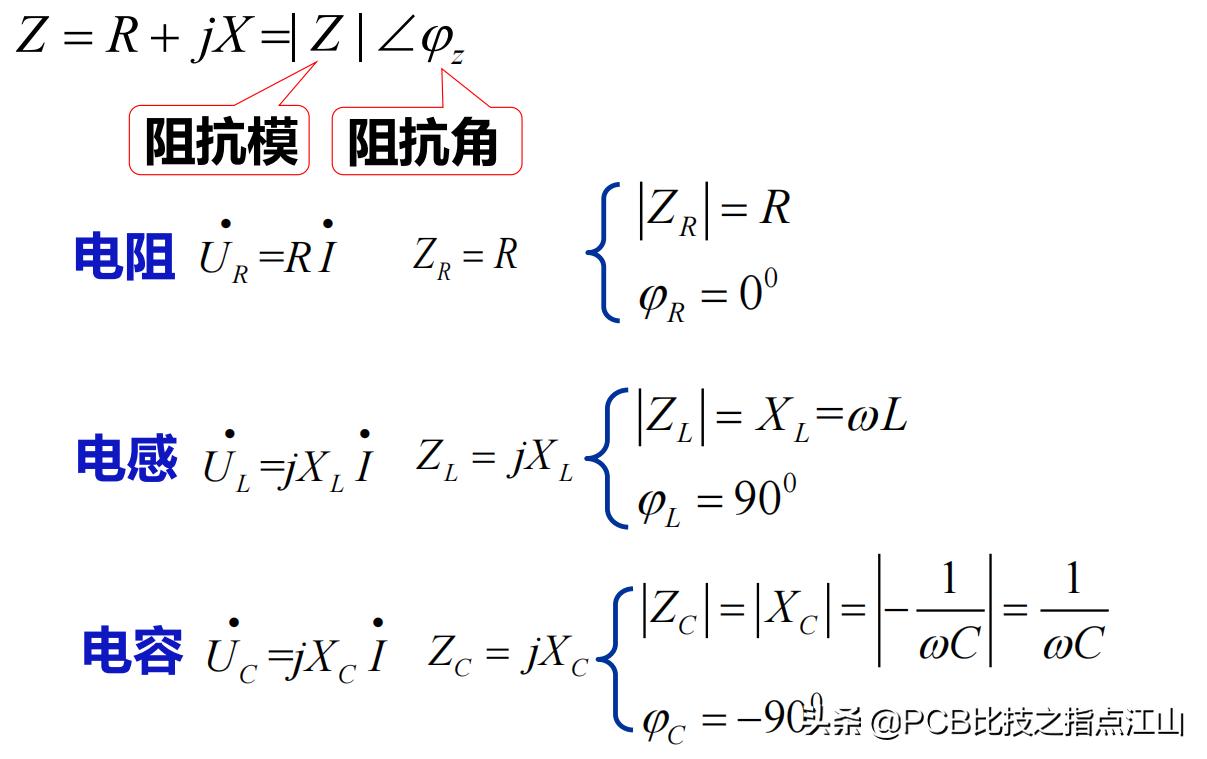

在印刷电路板(PCB)设计的复杂生态系统中,阻抗控制作为“隐形守护者”保障着信号完整性。它直接决定了高速、高频信号能否稳定传输而不失真,并且在5G通信、汽车电子和工业控制等领域是核心科技。除了大家熟知的差分阻抗和单端阻抗之外,PCB阻抗设计涵盖了根据不同应用场合定制的多种类型。每种类型都有其独特的结构特征、计算方法和应用边界。以下是结合实际应用案例和结构图对主要类型PCB阻抗设计的详细分析。

1. 单端阻抗设计:低速场景的“基本通用型”

单-ended阻抗设计是PCB阻抗控制的最基础形式,其结构由一根信号走线和一个作为回路的接地平面(或电源平面)组成。其核心是控制单个走线的特性阻抗,确保阻抗与源和负载(如芯片、连接器)匹配,以避免信号反射。

1.1 结构原则和关键影响因素

单端阻抗迹线依赖于“信号迹线 - 接地平面”结构来形成传输线。特性阻抗(\(Z_0\))主要受四个因素影响:

- 走线宽度 (W):在相同条件下,更宽的走线可以降低阻抗(导体面积增加,减少电阻和电容效应);

- 铜箔厚度 (T):更厚的铜箔(例如,70μm 而不是 35μm)通过增加导电横截面稍微降低了阻抗;

- 走线到接地平面的距离 (H):较小的 H 增大了走线和接地之间的电容,从而降低了阻抗;

- 衬底介电常数 (\(\epsilon_r\)):较高的 \(\epsilon_r\)(例如,FR-4 的 \(\epsilon_r\) ≈ 4.5 对比 PTFE 的 \(\epsilon_r\) ≈ 2.2)增加了走线与接地之间的电容,从而导致较低的阻抗。

1.2 计算公式和实际校准

For microstrip single-ended traces (trace on the PCB surface, ground plane below), the classic calculation formula is:

\(Z_0 = \frac{87}{\sqrt{\epsilon_r + 1.41}} \ln\left(\frac{5.98H}{0.8W + T}\right)\)

In actual design, since the formula is derived under ideal conditions (ignoring trace edge effects and substrate unevenness), calibration is required using professional software (such as Altium Designer's Impedance Calculator, Polar SI9000). For example, when designing a single-ended trace with \(Z_0\) = 50Ω on an FR-4 substrate (\(\epsilon_r\) = 4.5, H = 1.6mm), the calculated trace width W is approximately 1.2mm. However, considering the edge effect of the trace (the actual dielectric constant near the trace edge is lower than the bulk material), the actual width needs to be adjusted to 1.1mm to achieve the target impedance.

1.3 应用场景和优势

单端阻抗设计因其简单的结构和低成本而在低速、低频电路(信号频率≤100MHz,传输速率≤100Mbps)中被广泛使用,典型应用包括:

- 消费电子产品:Arduino开发板(将微控制器连接到GPIO引脚),电视遥控器电路板(按钮和芯片之间的信号传输);

- 工业控制:传感器信号线(例如,温度传感器 DS18B20 输出走线)、继电器控制信号线;

- 汽车电子:车载娱乐系统控制线(例如,CD 播放器按钮信号路径)。

它的主要优点是:

- 简单布局:对于单个信号只需要一条迹线,节省PCB空间(对紧凑型消费产品至关重要);

- 低成本:无需配对迹线对准或屏蔽结构,降低设计和制造的复杂性;

- 成熟工艺:兼容普通的PCB制造工艺(不需要特殊的蚀刻或层压工艺)。

1.4 插图

**

该图显示了单端微带线的横截面图。红色部分是35微米厚的铜线(W = 1.1毫米),灰色部分是FR-4基板(H = 1.6毫米,\(\epsilon_r\) = 4.5),绿色部分是接地平面。信号沿着线流动,返回电流通过接地平面形成回路(返回电流集中在在线正下方的区域,称为“皮肤效应”)。

2. 差分阻抗设计:抗干扰的“高速芯型”

差分阻抗设计使用两个紧密间距的平行信号走线来传输差分信号(两个具有相同幅度且相位相反的信号)。其核心是控制这两个走线之间的差分阻抗(\(Z_{diff}\)),并且它依靠“共模噪声抵消”效应来实现高抗干扰性能,使其成为高速信号传输的首选方案。

2.1 结构原理和共模噪声消除机制

差分对由两个具有相同阻抗的走线(走线A和走线B)组成。当传输信号时:

- 迹线A传输信号\(V_{in}\),迹线B传输信号\(-V_{in}\);

- 外部干扰(如相邻走线的电磁辐射)在两条走线上产生相同的共模噪声 \(V_n\);

- 在接收端,通过计算两条迹线之间的差值恢复信号:\((V_{in} + V_n) - (-V_{in} + V_n) = 2V_{in}\),并且共模噪声 \(V_n\) 完全被消除。

这种机制使差分对在复杂的电磁环境中(例如在5G基站或汽车ECU内部)也能保持信号完整性。

2.2 差分对的类型和阻抗计算

差分对根据其在印刷电路板上的位置分为两种结构形式:

2.2.1 微带差分对(表面贴装)

两条信号线位于PCB表面,下面有一个地平面。差分阻抗计算公式是:

\(Z_{diff} = 2Z_0(1 - k)\)

其中 \(Z_0\) 是单条走线的单端阻抗,\(k\) 是耦合系数(范围从 0.1 到 0.3,取决于走线间距 \(S\):较小的 \(S\) 增大 \(k\))。

2.2.2 坡道差分对(嵌入式)

两条迹线嵌入在两个接地平面之间,具有更好的屏蔽性能。计算公式是:

\(Z_{diff} = \frac{120}{\sqrt{\epsilon_r}} \ln\left(\frac{2B}{0.8W + T}\right) \times (1 - k)\)

其中 \(B\) 是上地平面和下地平面之间的距离。

In practical design, common differential impedance standards include 90Ω (Ethernet, HDMI 2.0), 100Ω (USB 3.0, PCIe 4.0), and 110Ω (SATA III). For example, when designing a PCIe 4.0 differential pair on an FR-4 substrate (\(\epsilon_r\) = 4.5, B = 2.0mm), the trace width W is 0.8mm, the spacing S is 1.2mm, and the calculated \(Z_{diff}\) is approximately 100Ω.

2.3 Application Scenarios and Key Design Notes

Differential impedance design is the core of high-speed signal transmission (transmission rate ≥ 1Gbps, frequency ≥ 1GHz), and its typical applications include:

- Communication interfaces: USB 4.0 (10Gbps), HDMI 2.1 (48Gbps), Ethernet 10GBASE-T (10Gbps);

- High-performance computing: PCIe 5.0 (32Gbps) in server motherboards, DDR5 memory differential pairs;

- Automotive electronics: Automotive Ethernet (100BASE-T1, 1000BASE-T1) for autonomous driving domain controllers.

Key design notes to avoid performance degradation:

- Equal length: The length difference between the two traces of the differential pair must be ≤ 5mil (0.127mm) to prevent signal skew (time delay between the two signals);

- Parallel routing: Avoid bending or branching the differential pair (bending will change the spacing S, leading to impedance discontinuity);

- Ground protection: Add ground vias every 500mil (12.7mm) on both sides of the differential pair to enhance shielding and reduce crosstalk.

2.4 Illustration

**

The diagram shows a top view (left) and cross-section (right) of a stripline differential pair. The two red traces (W = 0.8mm, S = 1.2mm) are embedded between two green ground planes (B = 2.0mm). The blue arrows indicate the direction of the differential signals (opposite phases), and the black dots represent ground vias for shielding.

3. Stripline Impedance Design: The "High-Frequency Shielded Type" for Anti-Interference

Stripline impedance design refers to a transmission line structure where the signal trace is completely embedded between two parallel ground planes (or one ground plane and one power plane). It belongs to a "fully shielded" transmission line, with excellent anti-electromagnetic interference (EMI) and anti-crosstalk capabilities, making it suitable for high-frequency analog signals (such as RF signals) and sensitive high-speed digital signals.

3.1 Structural Advantages and Performance Characteristics

Compared with microstrip lines (surface-mounted), stripline has three core advantages:

- Complete shielding: The upper and lower ground planes form a "Faraday cage" around the trace, blocking external EMI and preventing the trace from radiating electromagnetic energy outward;

- Stable impedance: Not affected by the external environment (such as dust, moisture on the PCB surface), and the impedance fluctuation range is ≤ ±3% (microstrip lines may have ±5% fluctuation);

- Low crosstalk: The shielded structure reduces the coupling between adjacent traces. For example, the crosstalk between two striplines 2mm apart is 15dB lower than that of microstrip lines.

3.2 Impedance Calculation and Material Matching

For a single-ended stripline (common in RF circuits), the characteristic impedance calculation formula is:

\(Z_0 = \frac{60}{\sqrt{\epsilon_r}} \ln\left(\frac{2B}{0.8W + T}\right)\)

where \(B\) is the distance between the two ground planes (equal to the total thickness of the substrate between the upper and lower grounds).

In high-frequency applications (such as 5G RF modules), the substrate material must be matched with the stripline. For example, when designing a 50Ω stripline for a 28GHz millimeter-wave signal, a PTFE substrate (\(\epsilon_r\) = 2.2, Df = 0.0005) is selected instead of FR-4 (Df = 0.02) to reduce signal attenuation (the attenuation of PTFE at 28GHz is only 1/4 of FR-4).

3.3 Application Scenarios and Process Requirements

Stripline impedance design is mainly used in scenarios with strict requirements for EMI and signal stability:

- RF communication: 5G base station RF modules (connecting transceivers to filters), satellite communication equipment (L-band, Ku-band signal lines);

- Test and measurement instruments: Oscilloscope probe lines (requiring low noise and high signal fidelity), signal generator output lines;

- Medical equipment: MRI machine control circuits (resisting strong magnetic field interference), ultrasonic probe signal lines.

The manufacturing process of stripline has higher requirements:

- Substrate uniformity: The thickness deviation of the substrate between the two ground planes must be ≤ 5% (otherwise, the impedance will be uneven);

- Layer alignment: The upper and lower ground planes must be strictly parallel, with an alignment error ≤ 25μm (preventing the trace from being offset and the shielding effect from being reduced);

- Via processing: Ground vias connecting the upper and lower ground planes must be arranged densely (every 300mil) to ensure the two ground planes are at the same potential.

3.4 Illustration

**

The cross-sectional view shows the stripline structure: the yellow signal trace (W = 0.6mm, T = 35μm) is embedded in the gray PTFE substrate (\(\epsilon_r\) = 2.2), with green upper and lower ground planes (B = 1.8mm). The black vias are ground vias connecting the two ground planes, forming a closed shielding structure. The red arrow indicates the high-frequency RF signal transmission direction.

4. Microstrip Impedance Design: The "Cost-Effective Type" for Versatile Applications

Microstrip impedance design is a transmission line structure where the signal trace is located on the surface of the PCB, with a single ground plane (or power plane) parallel to it below the substrate. It is the most widely used impedance design type in PCB engineering, balancing performance, cost, and manufacturability.

4.1 Structural Characteristics and Performance Trade-Offs

The microstrip line has a "semi-open" structure (the trace is exposed to the air), which leads to a trade-off between performance and cost:

- Advantages: Simple manufacturing (no need for embedding between layers), easy visual inspection (convenient for debugging and maintenance), and low cost (compatible with ordinary single-sided/double-sided PCB processes);

- Disadvantages: Poor EMI resistance (the exposed trace radiates electromagnetic energy), affected by the external environment (air's \(\epsilon_r\) ≈ 1, which will change the overall dielectric constant if there is moisture or dust, leading to impedance fluctuations), and higher crosstalk than stripline.

To make up for these shortcomings, microstrip lines are often optimized with "grounding vias" (adding vias on both sides of the trace to connect to the ground plane) or "shielding covers" (adding metal covers above the trace) in practical applications.

4.2 Impedance Calculation and Engineering Optimization

The characteristic impedance calculation formula for microstrip lines is the same as that for single-ended microstrip traces (mentioned in Section 1.2). However, since the trace is exposed to air, the actual dielectric constant (\(\epsilon_{eff}\)) is a weighted average of the substrate's \(\epsilon_r\) and air's \(\epsilon_r\) (≈1), so the formula needs to be adjusted for the effective dielectric constant:

\(\epsilon_{eff} = \frac{\epsilon_r + 1}{2} + \frac{\epsilon_r - 1}{2} \times \frac{1}{\sqrt{1 + \frac{12H}{W}}}\)

\(Z_0 = \frac{120\pi}{\sqrt{\epsilon_{eff}}} \times \frac{1}{\frac{W}{H} + 1.393 + 0.667\ln\left(\frac{W}{H} + 1.444\right)}\)

In engineering, for example, when designing a 75Ω microstrip line for a video signal (HDMI video channel) on an FR-4 substrate (\(\epsilon_r\) = 4.5, H = 1.2mm), the calculated W is 2.0mm. To reduce EMI, a ground via (diameter 0.3mm) is added every 400mil on both sides of the trace, and the distance between the via and the trace is 0.5mm (to avoid affecting the trace's impedance).

4.3 Application Scenarios and Typical Cases

Microstrip impedance design is suitable for most medium-speed, medium-frequency scenarios (transmission rate 100Mbps-1Gbps, frequency 100MHz-1GHz), and its typical applications include:

- 消费电子产品:笔记本液晶屏幕信号线(75Ω 微带线),智能手机相机模块信号线(50Ω 微带线);

- 汽车电子:车载信息娱乐系统LVDS信号线(100Ω差分微带对),仪表板显示信号线;

- 工业电子:PLC(可编程逻辑控制器)模拟信号线(4-20mA电流信号,50Ω微带线)。

一个典型的例子是为一个Wi-Fi 6模块(2.4GHz/5GHz)设计一个50Ω微带线。该模块使用FR-4基板(H = 0.8mm),走线宽度W = 0.8mm,并在走线周围添加了接地通孔。这个设计确保了

Single - Ended Impedance Standards

- Impedance Values: In most general - purpose applications, a 50 - ohm single - ended impedance is a widely - adopted standard. This value is favored because it offers a good balance between minimizing signal reflection and being compatible with a vast array of components, such as many integrated circuits, connectors, and test equipment. For example, in RF (Radio Frequency) circuits, 50 - ohm traces are common as they match the output impedance of most RF sources and loads, ensuring efficient power transfer. In addition to 50 - ohms, 75 - ohm single - ended impedance is also used in specific applications, particularly in video signal transmission. Video coaxial cables, for instance, often have a characteristic impedance of 75 ohms. When designing PCB traces for video signals (like composite video or some digital video interfaces in legacy systems), the single - ended impedance of the PCB trace may be designed to match this 75 - ohm standard to prevent signal degradation.

- Tolerance: The industry typically aims for a tight tolerance in single - ended impedance. A tolerance of ±5% is common in high - performance applications, while in less - critical scenarios, a tolerance of up to ±10% might be acceptable. For example, in a consumer electronics device where the cost - performance balance is crucial, a ±10% tolerance might be sufficient for single - ended impedance on non - high - speed signal traces. However, in aerospace or medical equipment, where signal integrity is of utmost importance, a ±5% or even tighter tolerance is required.

Differential Impedance Standards

- Impedance Values: For high - speed digital interfaces, specific differential impedance values are standardized. In USB 3.0 and PCIe 4.0, a differential impedance of 100 ohms is the standard. This is because these interfaces operate at high data rates (up to 10 Gbps in USB 3.0 and 16 Gbps per lane in PCIe 4.0), and a 100 - ohm differential impedance helps in maintaining signal integrity by reducing crosstalk and ensuring proper signal transmission. Ethernet interfaces also often adhere to a differential impedance standard. For 10GBASE - T Ethernet, a differential impedance of 100 ohms is typical. This standard is crucial for reliable data transmission over twisted - pair cables connected to the PCB, as it ensures compatibility with the Ethernet cabling system and minimizes signal reflections. HDMI 2.0 has a differential impedance standard of 90 ohms. Given the high - bandwidth video and audio signals it transmits (supporting up to 18 Gbps data rate), this 90 - ohm differential impedance helps in achieving the required signal quality and integrity for high - definition content delivery.

- Length Matching and Skew: In differential pair design, the length difference between the two traces in a pair must be minimized. The industry standard for length skew in high - speed applications is typically ≤5 mils (0.127 mm). For example, in high - performance computing systems, where data transfer rates are extremely high (such as in server motherboards with PCIe 5.0 interfaces running at 32 Gbps per lane), maintaining this low skew is crucial. Even a small skew can cause signal misalignment at the receiving end, leading to data errors.

Stripline and Microstrip - Specific Standards

- Stripline:

- Shielding and Layer Alignment: In stripline design, especially for high - frequency applications like 5G RF modules, the shielding provided by the upper and lower ground planes is critical. The alignment tolerance between the upper and lower ground planes should be within ≤25μm. This ensures that the signal trace is properly centered between the ground planes, maintaining the integrity of the "Faraday cage" - like shielding structure. Any misalignment can lead to uneven impedance and increased susceptibility to electromagnetic interference. The substrate thickness uniformity between the two ground planes is also tightly controlled. A thickness deviation of ≤5% is required to ensure consistent impedance along the stripline. In 5G base station RF modules operating at frequencies such as 28 GHz or 39 GHz, where signal attenuation and interference are major concerns, this strict control over substrate thickness is essential for maintaining signal quality.

- Via Placement: Ground vias connecting the upper and lower ground planes in stripline designs should be placed densely. A common standard is to place them every 300 mils. This ensures that the two ground planes are at the same potential, enhancing the shielding effectiveness and reducing the likelihood of ground - related signal issues.

- Microstrip:

- Grounding and Isolation: To mitigate the drawbacks of its semi - open structure, microstrip lines often incorporate grounding vias. In applications where electromagnetic interference (EMI) is a concern, such as in Wi - Fi modules operating in the 2.4 GHz and 5 GHz bands, ground vias are added at regular intervals. A standard practice is to add a ground via (with a diameter typically around 0.3 mm) every 400 mils on both sides of the trace, with a distance of 0.5 mm between the via and the trace to avoid affecting the trace impedance. This helps in reducing EMI radiation from the microstrip trace. When microstrip lines are used in close proximity to other sensitive components or traces, isolation standards come into play. The distance between microstrip lines and other traces or components should be sufficient to minimize crosstalk. A general rule - of - thumb is to maintain a distance of at least 3 times the width of the microstrip trace from other conductors to reduce the risk of crosstalk.

Material - Related Standards

- Dielectric Constant (\(\epsilon_r\)) and Loss Tangent (Df): In high - frequency applications, the choice of substrate material is crucial. For example, in 5G communication and high - speed computing, materials with low dielectric constant (\(\epsilon_r\)) and low loss tangent (Df) are preferred. PTFE (Polytetrafluoroethylene) with an \(\epsilon_r\) of around 2.2 and a Df of 0.0005 is often used in 5G RF modules. The low \(\epsilon_r\) helps in reducing signal attenuation, while the low Df minimizes power loss in the form of heat dissipation. In contrast, traditional FR - 4 materials with an \(\epsilon_r\) of approximately 4.5 and a relatively higher Df (around 0.02) are more suitable for lower - frequency applications. When designing PCBs for automotive electronics, which may operate at a range of frequencies, the material selection also needs to consider environmental factors. Materials used in automotive applications should have good thermal stability and mechanical strength in addition to appropriate electrical properties. For example, some modified epoxy - based materials with enhanced thermal characteristics are used in automotive PCBs to withstand the harsh temperature conditions inside a vehicle.

- Copper Foil Thickness: The thickness of the copper foil used in PCB traces can also be standardized based on the application. For general - purpose PCB designs, 1 oz (35μm) copper foil is commonly used. However, in applications where higher current - carrying capacity is required, such as in power - related traces in some industrial control boards or high - power amplifier circuits in RF systems, 2 oz (70μm) or even thicker copper foil may be specified. Thicker copper foil reduces the resistance of the trace, allowing for more efficient power transfer and minimizing power losses in the form of heat generation.

Testing and Validation Standards

- Time - Domain Reflectometry (TDR): TDR is a widely used technique for testing PCB impedance. The industry standard for TDR testing requires accurate measurement of impedance along the length of the trace. The TDR equipment should be able to resolve impedance variations with a high degree of precision, typically within ±1 ohm for high - quality PCB designs. This allows for the detection of any impedance discontinuities, such as those caused by trace width changes, vias, or poor solder joints. For example, in a high - speed data transmission line, a TDR test can identify a small impedance bump that could potentially cause signal reflections and degrade the overall signal quality.

- Frequency - Domain Analysis: In addition to TDR, frequency - domain analysis using vector network analyzers (VNAs) is also an important testing method. VNAs can measure the insertion loss, return loss, and impedance of PCB traces over a wide frequency range. The industry standard for frequency - domain analysis in high - speed and high - frequency PCB designs requires measurement accuracy within a certain dB range for insertion and return loss. For example, in a 5G antenna feed line, the insertion loss measured by a VNA should be within a specified range (e.g., ≤0.5 dB) over the operating frequency band of the 5G system to ensure efficient power transfer from the transmitter to the antenna.